Le modèle de von Neumann

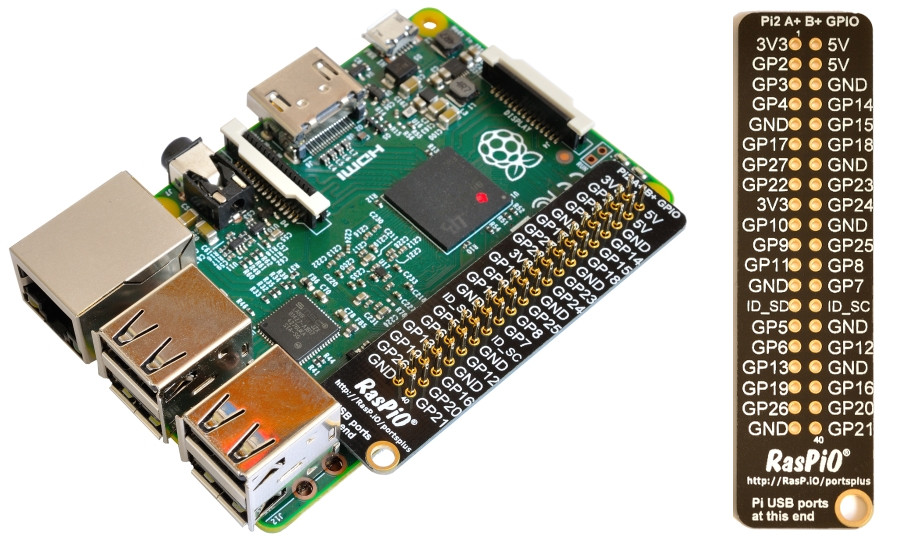

- Architecture proposée par John von Neumann en 1945

- Pour le développement de l'ENIAC

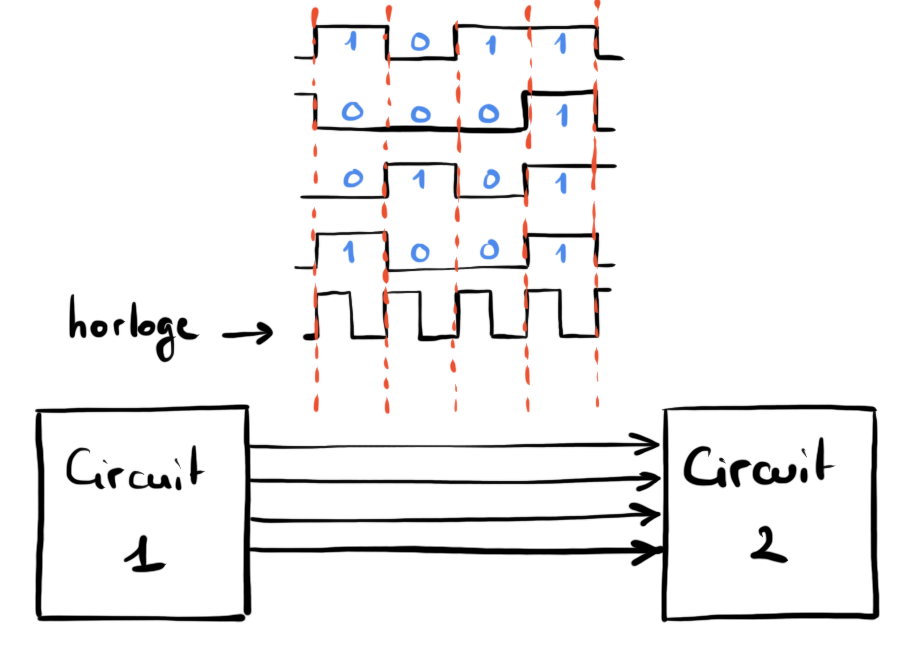

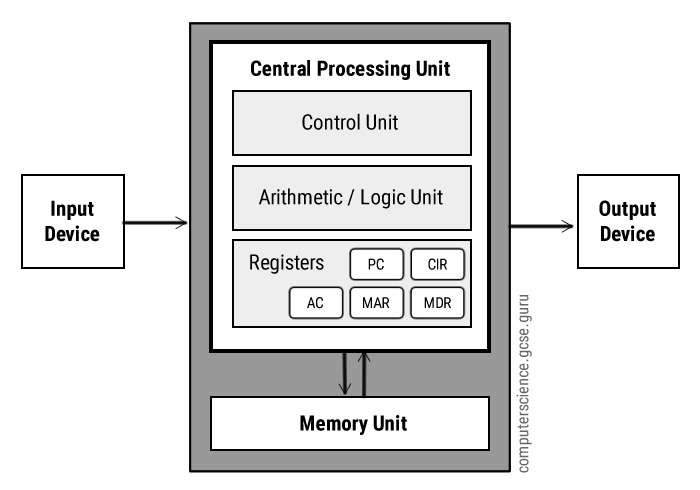

- Ordinateur à programme enregistré

- Données et instructions dans la même mémoire

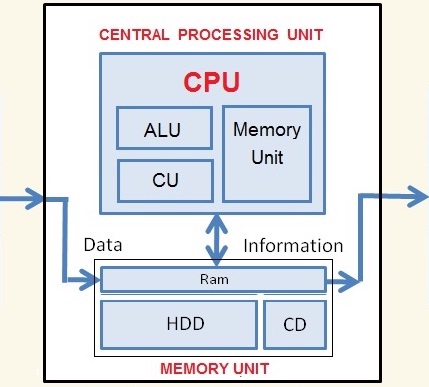

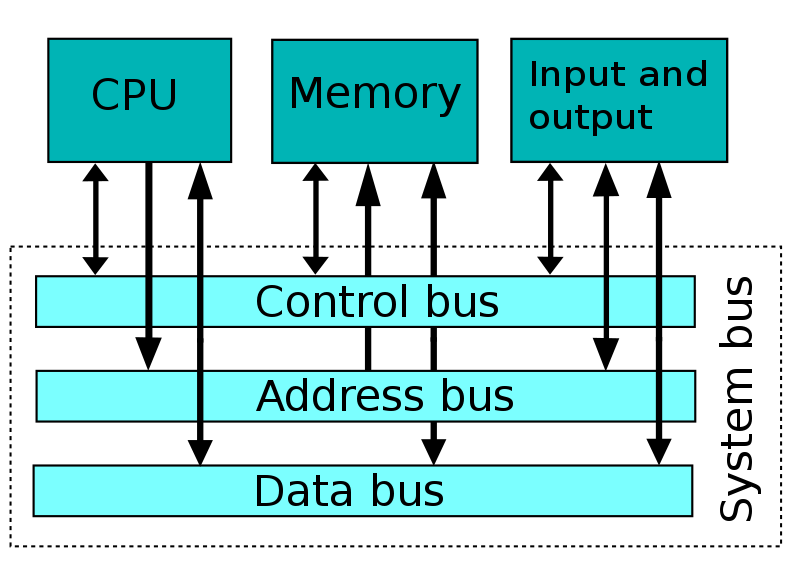

- 5 éléments principaux

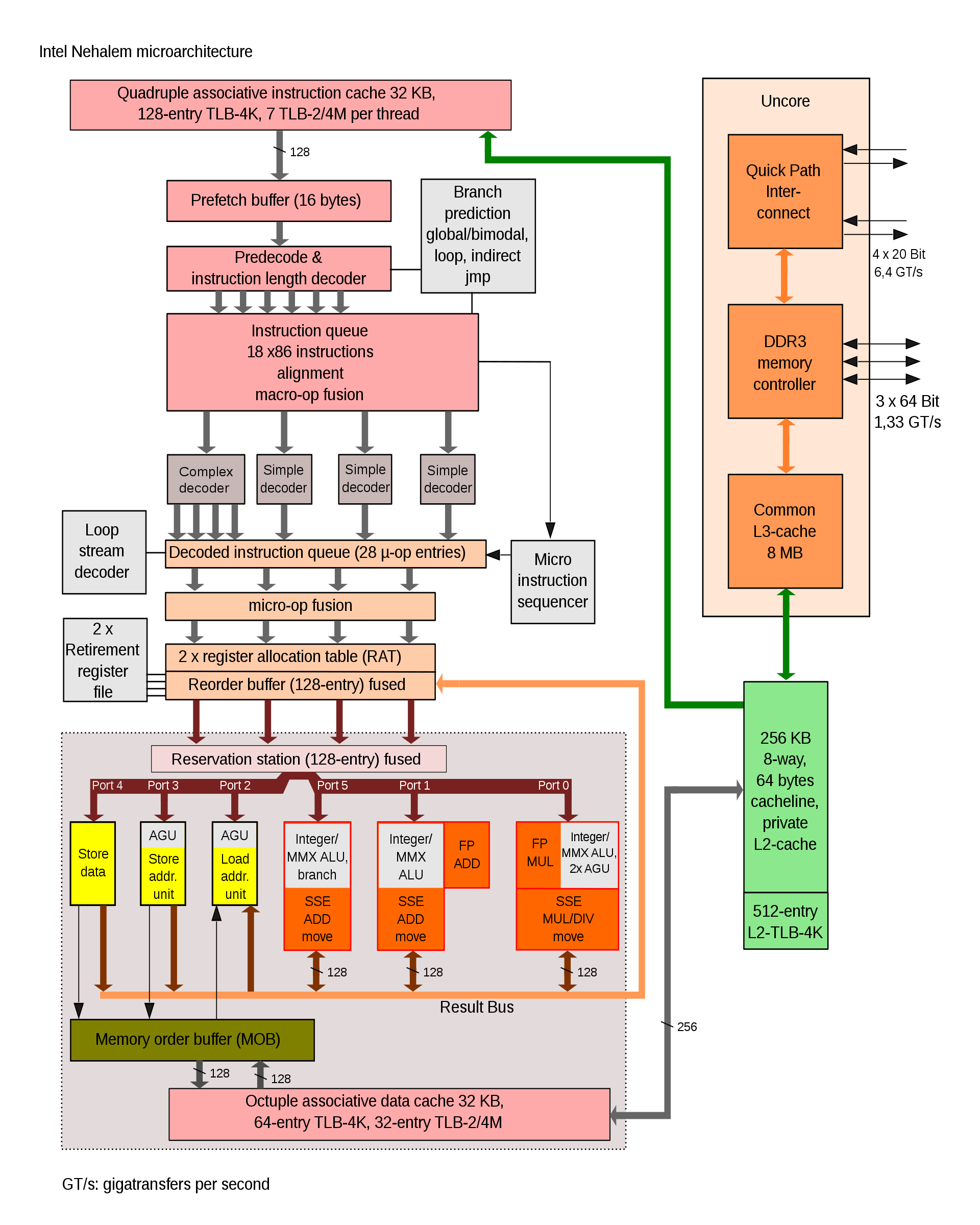

- Unité de calcul

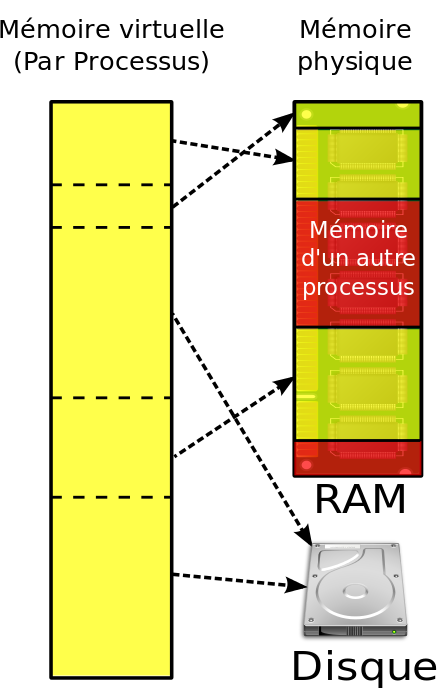

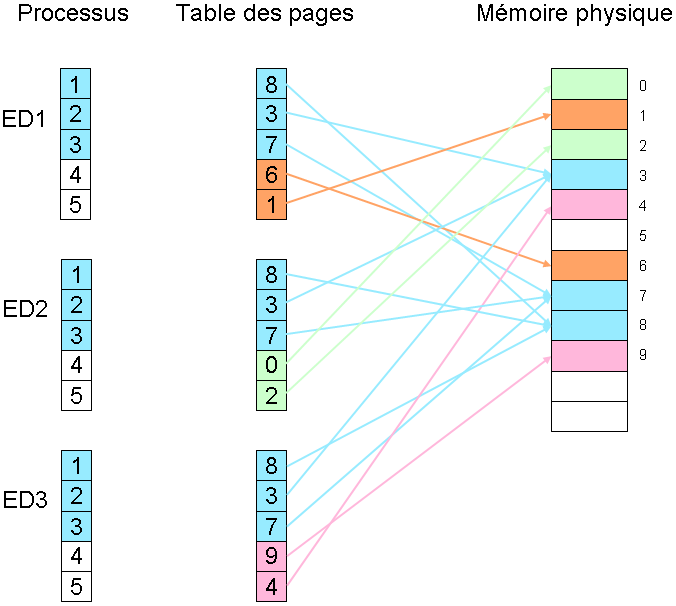

- Mémoire

- Unité de contrôle

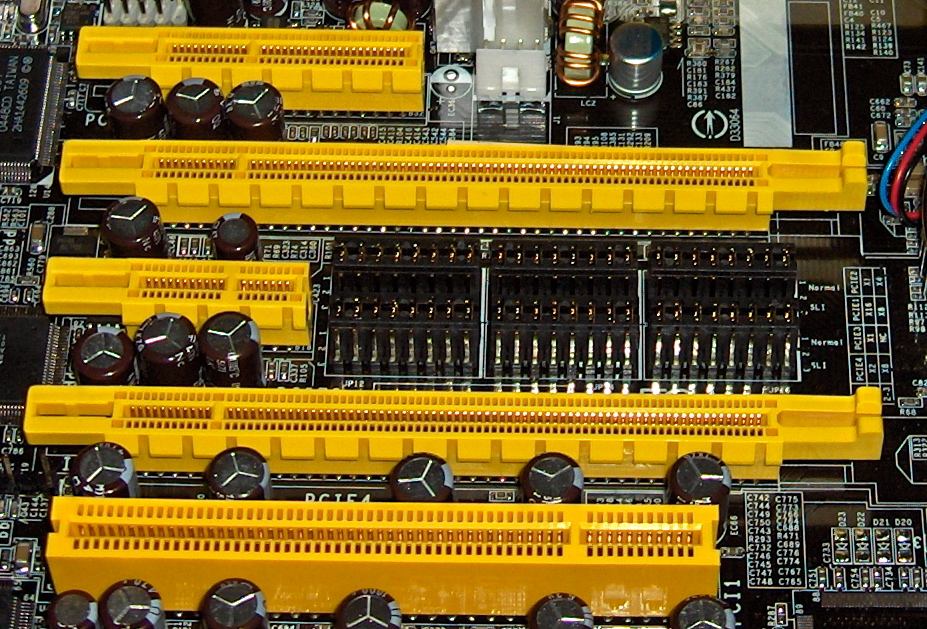

- Périphériques d'entrée

- Périphériques de sortie